1. Jurnal [Kembali]

Gambar Module D'Lorenzo

Gambar Jumper

1. Panel DL 2203C.

2. Panel DL 2203D.

3. Panel DL 2203S.

4. Jumper

4. Prinsip Kerja Rangkaian [Kembali]

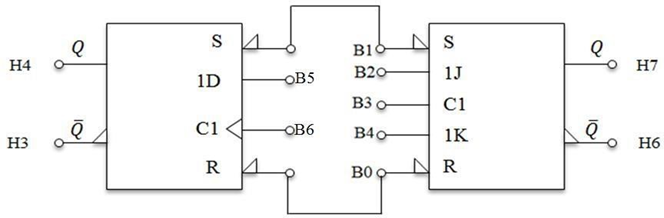

Pada percobaan 1 yaitu kita diminta untuk membuat rangkaian menggunakan JK flip-flop dan D flip-flop. Pada switch SPDT kaki high SPDT terhubung ke vcc dan kaki low SPDT terhubung ke ground. Pada JK flip - flop, kaki B1 terhubung ke pin S (set). Selanjutnya pada B2 terhubung ke pin J , B3 terhubung ke CLK, B4 terhubung ke pin K dan B0 terhubung ke pin R (reset). Seperti pada jurnal percobaan, ketika diberikan input B6 ,B5,B4,B3 dan B2 = dont'care, dan B1 = 1 B0 = 0 maka nilai keluaran Q = 0 dan Q' = 1. Sesuai dengan tabel kebenarannya, ketika B4,B3, dan B2 don't care dan hanya diketahui nilai B0 dan B1 maka pada ic JK fliplop tidak mempengaruhi nilai keluarannya. Sehingga ketika diberikan input B1 = 1 B0 = 0 rangkaian dalam keadaaan reset.

Selanjutnya pada ic 7474 menggunakan D flip - flop. Pada ic ini memiliki 2 flip-flop yaitu RS flip-flop dan D flip-flop. Kaki B5 terhubung ke pin D dan kaki B6 terhubung ke pin CLK. D flip flop memiliki prinsip kerja sama seperti RS flip-flop namun inputan R terlebih dahulu diberi gerbang NOT. Sehingga ketika nilai D = 0 maka nilai Q = 0. Dapat dilihat pada jurnal percobaan diberikan input B6 ,B5,B4,B3 dan B2 = dont'care, dan B1 = 1 B0 = 0. Maka nilai pada D flip flop yaitu 0 sehingga untuk ouput dipengaruhi oleh RS flip-flop sdengan nilai keluarannya yaitu Q=0 dan Q'=1.

6. Analisa [Kembali]

Download file HTML [disini]

Download file video simulasi [disini]

Download datasheet 74LS112 [disini]

Download datasheet 7474 [disini]

.jpg)

Tidak ada komentar:

Posting Komentar